# Design and Implementation of Five Level Diode **Clamped Inverter**

Riya G. Barapatre<sup>1</sup>, Sachin Y.Thengari<sup>1</sup>, Samir D.Landge<sup>1</sup>, Shubhendu B.Mukherji<sup>1</sup>, Vishnu S. Gandla<sup>1</sup>, Yogesh N. Zade<sup>1</sup> Prof.U.E.Hiwase<sup>2</sup>

> <sup>1</sup>Students, Dept. of Electrical Engineering, <sup>2</sup>Assistant Professor, Dept. of Electrical Engineering Priyadarshini College of Engineering, Nagpur, India, 440016

Abstract-Multilevel inverter is a very versatile technology and latest advancement in power electronics. This paper presents a five level diode clamped multilevel inverter topology which can be used for low medium power industrial applications and studied that how it reduces harmonic distortion. Most of the times for efficient control of industrial drives, inverters are used and various sources of electrical energy are employed. As the number of voltage levels increases, the output voltage appears to be a staircase waveform, which will reduce harmonic distortion. However, high number of levels increases the control complexity and introduce voltage imbalance. A pulse to the inverter is provided using discontinuous PWM technique.

Keywords- PWM Technique, Diode Clamped Multilevel Inverter, Total Harmonic Distortion.

#### ACKNOWLEDGEMENT

We take this opportunity with great pleasure to express our sincere regards and keep sense of gratitude to our guide Mr. U. E.Hiwse , Professor, Priyadarshani college of Engineering for his valuable guidance and support for the Project. This project is the reflection of his ideas, thoughts, concepts to make this project stand where it is today. We would like to thank him for providing excellent academic climate in the institution and encouragement and suggestions.

# INTRODUCTION

Multilevel Inverters have gained much attention in the field of the medium voltage and high power applications because of their many advantages, such as their low voltage stress on power switches, low harmonic and EMI output. At present, there are three basic multilevel inverter topologies: diode-clamped multilevel inverter (DCMI), flying capacitor multilevel inverter (FCMI) and multi-module cascaded inverter (MMCI). The diode clamped multilevel inverter was also called the neutral point clamped (NPC) inverter. When it was first used in a three-level inverter in which the mid voltage level was defined as the neutral point because the NPC inverter effectively doubles the device voltage levels without requiring precise voltage matching. Among Various Modulation Technique such as PWM, SPWM, SVPWM, MPWM. SPWM Technique is more prominent over other due to following merits. It proportionally varies the width of each pulse to the amplitude of a sine wave evaluated at thecenter of the same pulse.

# II- METHODOLOGY

## (a).Diode Clamped Multi-level Inverter

Numerous industrial applications have begun to require higher power apparatus in recent years. Some medium voltage motor drives and utility applications require medium voltage and megawatt power level. For a medium voltage grid, it is troublesome to connect only one power semiconductor switch directly. As a result, a multilevel power converter structure has been introduced as an alternative in high power and medium voltage situations. A multilevel converter not only achieves high power ratings, but also enables the use of renewable energy sources. Renewable energy sources such as photovoltaic, wind, and fuel cells can be easily interfaced to a multilevel converter

# National Conference on "Recent Trends in Electrical Engineering" NCRTEE-19 Organized by Electrical Engineering Department, Priyadarshini College of Engineering, Nagpur-19 International Journal of Innovations in Engineering and Science, Vol. 4, No.7, 2019 www.ijies.net

system for a high power application. The concept of multilevel converters has been introduced by NABE- EL Since 1975. The various advantages of multi-level inverter are, they can generate output voltages with extremely low distortion and lower dv/dt, they draw input current with very low distortion, they generate smaller common-mode (cm) voltage, thus reducing the stress in the motor bearings, they can operate with a lower switching frequency. The diode clamped multilevel inverter was also called the neutral point clamped (NPC) inverter. When it was first used in a three-level inverter in which the mid voltage level was defined as the neutral point because the NPC inverter effectively doubles the device voltage levels without requiring precise voltage matching.

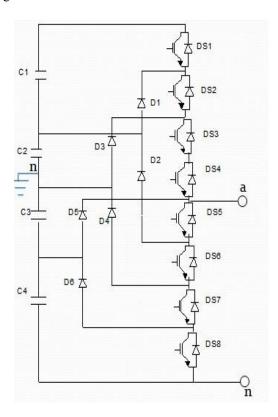

Number of DC bus capacitor in a multi level inverter is decided by (n-1), Number of switches in Multilevel inverter is decided by 2\*(n-1), Voltage source is decided by Vdc/ (n-1) & clamping diode is given by (n-1)\*(n-2). Where 'n' is number of level of an inverter. For a five level inverter shown in "fig.1".

Fig. 1. Five level diode clamped inverter circuit

Table 1. Switching States Diode Clamped five Level Inverter

| Switching states | Output<br>voltages | D<br>S<br>1 | D<br>S<br>2 | D<br>S<br>3 | D<br>S<br>4 | D<br>S<br>5 | D<br>S<br>6 | D<br>S<br>7 | D<br>S<br>8 |

|------------------|--------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| +1               | Vdc/2              | 1           | 1           | 1           | 1           | 0           | 0           | 0           | 0           |

| +2               | Vdc/4              | 0           | 1           | 1           | 1           | 1           | 0           | 0           | 0           |

| 0                | 0                  | 0           | 0           | 1           | 1           | 1           | 1           | 0           | 0           |

| -2               | -Vdc/4             | 0           | 0           | 0           | 1           | 1           | 1           | 1           | 0           |

| -1               | -Vdc/2             | 0           | 0           | 0           | 0           | 1           | 1           | 1           | 1           |

In this circuit, the DC bus voltage is split up in to three levels as shown. Five-level diode-clamped converter in which the DC bus consist of four capacitor C1,C2,C3,C4 for DC bus voltage Vdc, the voltage across each capacitor is Vdc/4 & each device voltage stress will be limited to one capacitor voltage levels Vdc/4 through clamping diodes, For voltage levels Van= Vdc/2 turn on all upper switches S1-S4, For voltage level Van= Vdc/4, turn on three upper switches S2-S4 and lower switch S5,For voltage level Van=0, turn on two upper switches S3 and S4 and two lower switches S5 and S6, For voltage levels Van= -Vdc/4, turn on one upper switch S4 and three lower switches S5-S7, For voltage levels Vdc/2, turn on all lower switches S5-S8 NPC inverter which has been extensively used today in industrial drives, traction as well as FACT's system Based on concept of using diodes to limit power devices voltage stress Output phase voltage can assume any voltage level by selecting any of the nodes

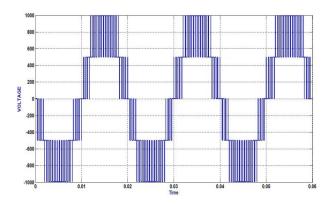

Fig.2. Output voltage of Diode Clamped Five level Inverter

# e-ISSN: 2456-3463 National Conference on "Recent Trends in Electrical Engineering" NCRTEE-19 Organized by Electrical Engineering Department, Priyadarshini College of Engineering, Nagpur-19 International Journal of Innovations in Engineering and Science, Vol. 4, No.7, 2019 www.ijies.net

DCMI is considered as a type of multiplexer that attaches the output to one of the available nodes Although main diodes have same voltage rating as main power devices, much lower current rating is allowable For three-phase DCMI, the capacitors need to filter only the high-order harmonics of the clamping diodes currents, low-order components intrinsically cancel each other Each power device block only a capacitor voltage Clamping diodes block reverse voltage.

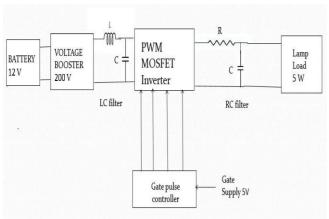

BLOCK DIAGRAM

# IV. HARDWARE DESIGN

#### (a). Hardware Circuit & Component:-

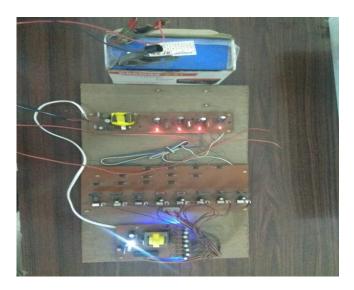

As per the proposed scheme, the hardware model of 5 level diode clamped inverter. In this prototype experiment setup of proposal multilevel boost inverter drive system.

The table enlist the component which are used in construction of hardware circuit with their specification.

| Sr. no | Components      | specification   |

|--------|-----------------|-----------------|

| 1      | Battery         | 7A/12V          |

| 2      | AC capacitor    | 2.2μF/250V      |

| 3      | DC capacitor    | 100μF/100V      |

| 4      | Inductor        | 8mH             |

| 5      | MOSFET          | IRF240 200V/18A |

| 6      | Driver IC       | TLP 250         |

| 7      | Microcontroller | AT tiny13 A     |

|        |                 | AT mega8        |

| 8      | Resistive load  | $10k\Omega$     |

# (b). Circuit Description:

The hardware circuit is divided into following units:

- 1) Battery

- 2) Multilevel boost converter

- 3) 5 level diode clamped inverter & load

- Gate driver circuit

### (1).Battery:

The battery can be charged by using PV charge controller which is connected with battery. The rating of battery is 7A/12V. A 12 V is the input to Boost Converter.

#### (2). Multilevel Boost Converter:

It is a DC-DC converter which is constructed using an inductor of 8 mH, MOSFET, 3 AC capacitor, 4 DC capacitor. AT tiny13 A microcontroller is used to generate the firing pulse for MOSFET by sensing the output voltage. The circuit of multilevel boost converter.

Impact Factor Value 4.046 e-ISSN: 2456-3463

National Conference on "Recent Trends in Electrical Engineering" NCRTEE-19 Organized by Electrical Engineering Department, Priyadarshini College of Engineering, Nagpur-19 International Journal of Innovations in Engineering and Science, Vol. 4, No.7, 2019 www.ijies.net

#### (3).Inverter & Load:

To construct a 5 level single phase inverter circuit, 8 MOSFET switches whose rating is IRF240(200V/18A) are used. A MOSFET/IGBT driver optically isolated TLP250 is used as driver IC. Isolated supplies are drawn and is given to driver of MOSFET.

## (4).Gate Driver Circuit:

A gate driver is a power amplifier that accepts a low power input from a controller IC and produces high current drive input for gate of high power transistor such as high power IGBT or power MOSFET. Gate driver can be provided either on chip or a discrete module. In essence of gate consist of level shifter in combination with amplifier.

#### V. RESULT (WAVEFORMSOF OUTPUT)

Under no load condition, the output of five level diode clamped multilevel inverter is shown fig. the peak value of inverter is 59.98V on either polarity.

Under load condition, the output of 5 level diode clamped multilevel inverter. The peak value of inverter is 60.01v on either polarity.

# CONCLUSION

The main objective of this paper is to provide a general notion about the multilevel power converters and various modulation strategies mainly PWM techniques and their applications. We deduced possible switching states in Five level diode clamped. The general concept of multilevel power conversion was introduced more than twenty years ago. However, most of the development in this area has occurred over the past five years. Furthermore, each year seems to bring even more publications than the previous. Besides the mainstream power electronics conferences and journals, multilevel power conversion is also showing up in power systems and electronics societies. Despite the rapid growth of this area in recent years and the increasing number of innovations introduced each year, there is still much more that can be done. And also This paper has provided a brief summary of multilevel inverter circuit topologies and their control strategies. Different applications using different inverter circuits were also discussed. As mentioned in Section I, an early patent for the cascaded multilevel inverter can be traced back to 1975. However, the commercial products that

# Impact Factor Value 4.046

National Conference on "Recent Trends in Electrical Engineering" NCRTEE-19

Organized by Electrical Engineering Department, Priyadarshini College of Engineering, Nagpur-19

International Journal of Innovations in Engineering and Science, Vol. 4, No.7, 2019

www.ijies.net

utilize this superior circuit topology were not available until the mid-1990s. Today, more and more commercial products are based on the multilevel inverter structure, and more and more worldwide research and development of multilevel inverter-related technologies is occurring.

This paper cannot cover or reference of all the related work, but the fundamental principle of different multilevel inverters has been introduced systematically. The intention of the paper was simply to provide groundwork to readers interested in looking back on the evolution of multilevel inverter technologies, and to consider where to go from here.

#### REFERENCE

e-ISSN: 2456-3463

- [1] J. Rodriguez, J. S. Lai and F. Z. Peng, "Multilevel Inverters: Survey of Topologies, Controls, and Applications," IEEE Transactions on Industry Applications, vol. 49, no. 4, Aug. 2002, pp. 724-738.

- [2] J. S. Lai and F. Z. Peng, "Multilevel Converters-A new Breed of Power Converters," IEEE Trans. Intraplate., vol.32,pp. 509-517, May/June 1996.

- [3] L. M. Tolbert, F. Z. Peng, and T. Habetler, "Multilevel Converters for Large Electric drives," IEEE Trans. Ind. Applicat.,vol.35,pp. 36-44, Jan./Feb. 1999.

- [4] R. H. Baker and L. H. Bannister, "Electric Power Converter," U.S. Patent 3 867 643, Feb. 1975.

- [5] A. Nabae, I. Takahashi, and H. Akagi, "A New Neutral-point Clamped PWM inverter," IEEE Trans. Intraplate., vol. IA-17, pp. 518-523, Sept./Oct. 1981.

- [6] IEEE Trans. Power Electr., Vol. 24, No.2, pp. 1-11, 2009.

- [7] Andrzej M. Trzynadiowski, "An Overviews of Modern PWM Techniques for Three-Phase, voltage-controlled, voltage source Inverters" in Proc. of the IEEE International Symposium on Industrial, (ISIE) '96, 17-20 June 1996 pp.25-31

- [8] J. S. Lai and F. Z. Peng, "Multilevel Converter-A New Breed of Power Converters, "IEEE Trans. Industry Applications, Vol. 32, No. 3, May/June 1996, pp., 509-517.